奇拉尔免安装绿色中文版

3.16G · 2025-10-11

引言:之前给大家介绍了芯片的制造和封装。今天这篇,我们来看看芯片的设计。

众所周知,芯片拥有极为复杂的结构。

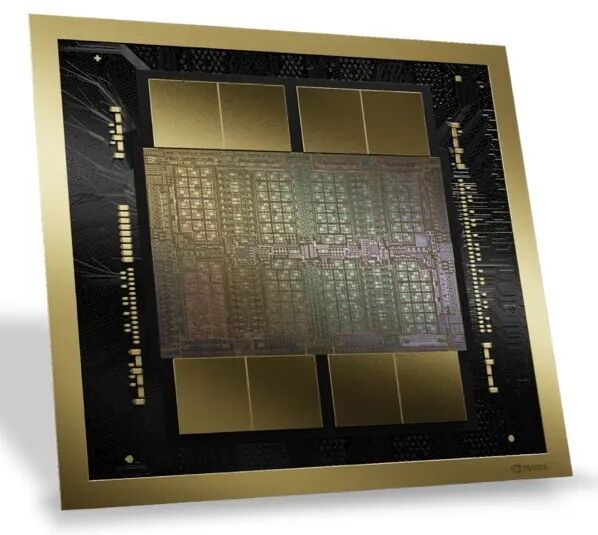

以英伟达的 B200 芯片为例,在巴掌大的面积上,塞入了 2080 亿个晶体管。里面的布局,堪称一个异次元空间级的迷宫。

如此复杂的架构,无论是制造还是设计,都具有极大的难度。

早期集成电路刚刚诞生的时候,晶体管的数量并不多,结构也不复杂。

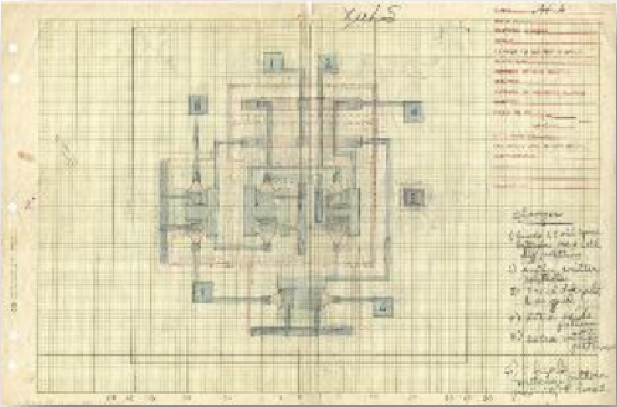

所以,基本上都是设计工程师直接在图纸上绘制电路的物理版图,然后把版图送到制造工厂,工厂进行生产。

他们手工绘制的版图是非常精细的,直接具体到了晶体管的物理层级,包括布局布线等。

随着集成电路变得越来越复杂,他们仍然采用这种方式,先画底层细节,然后进行“拼接”,最终组成一个完整的集成电路。

这种设计理念,叫做自底向上(Bottom-Up)设计。

这里就要说明一下,一颗芯片从设计的角度来看,是分为不同层级的。

从上到下,依次是:系统层、RTL 层、门级层、晶体管层、布局布线层、掩膜层。

系统层,是最高层,是站在整个宏观的角度对芯片进行整体设计。

RTL 层,是寄存器传输层(Register Transfer Level)。门级层的“门”,就是门电路。门电路是由晶体管搭建的。

掩模,在之前晶圆制造里介绍过,就是光掩模版,是芯片设计的最终产物,是最底层的、最能够从细节对芯片进行描述的东东。掩模层,是最底层。

自底向上(Bottom-Up)设计适用于早期的集成电路和 PCB 传统电路。

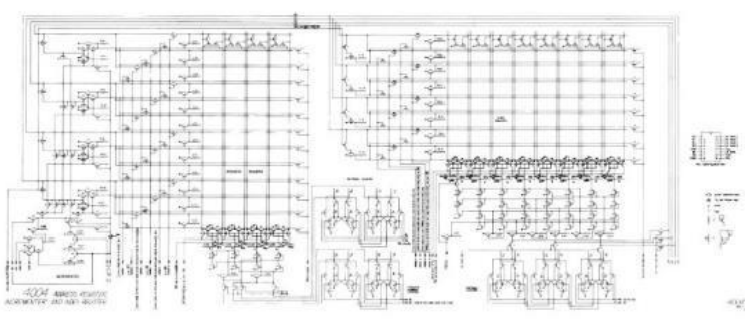

到了上世纪 70-80 年代,集成电路发展为大规模和超大规模集成电路,晶体管数量超过 1 万。

此时,再采用自底向上(Bottom-Up)方式就不合适了。于是,自顶向下(Top-Down)的设计理念开始崛起。

简单来说,就是不再从细节开始入手,而是“先宏观,再微观”—— 先做系统级设计,然后再做 RTL 级设计(逻辑功能设计)。等上层设计完成后,再进行下层设计(门级层、晶体管层、布局布线层和掩膜层),完善每一个细节。

自顶向下(Top-Down)设计理念一直到现在都是主流。对于日益复杂的芯片架构来说,这种方式具有更高的效率、更短的设计周期,以及更低的设计成本。

逐级的设计,伴随着逐级的仿真验证,所以,这种设计方式的成功率也很高。

工欲善其事,必先利其器。想要高效进行芯片的设计,当然不能一直依赖于手工作业。

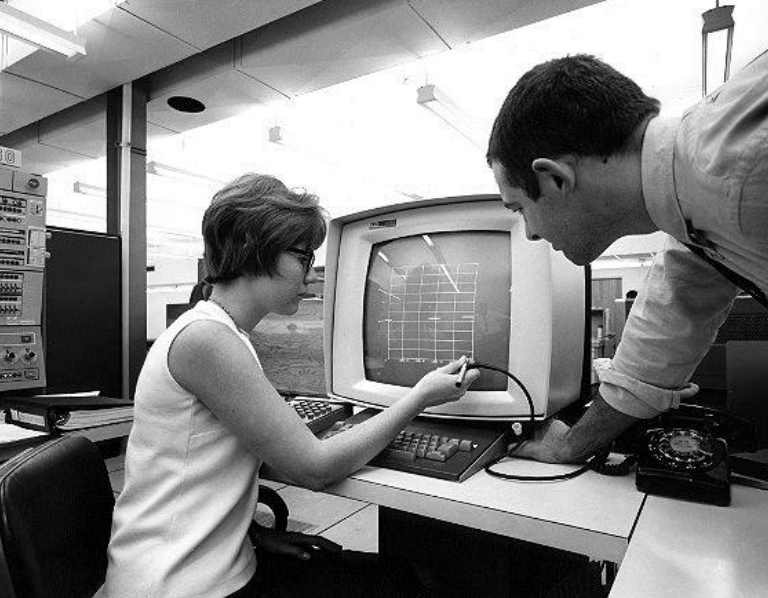

上世纪 70 年代,随着计算机技术的不断成熟,芯片设计逐渐从手工设计走向了计算机辅助设计阶段,出现了 ICCAD(IC Computer Aided Drafting)。

到了 80 年代,又出现了 CAE(Computer Aided Engineering,计算机辅助工程)。CAD 专注于产品设计建模与绘图,而 CAE 侧重于工程仿真与性能优化。

再后来,大名鼎鼎的 EDA(Electronic Design Automation,电子设计自动化)诞生了。

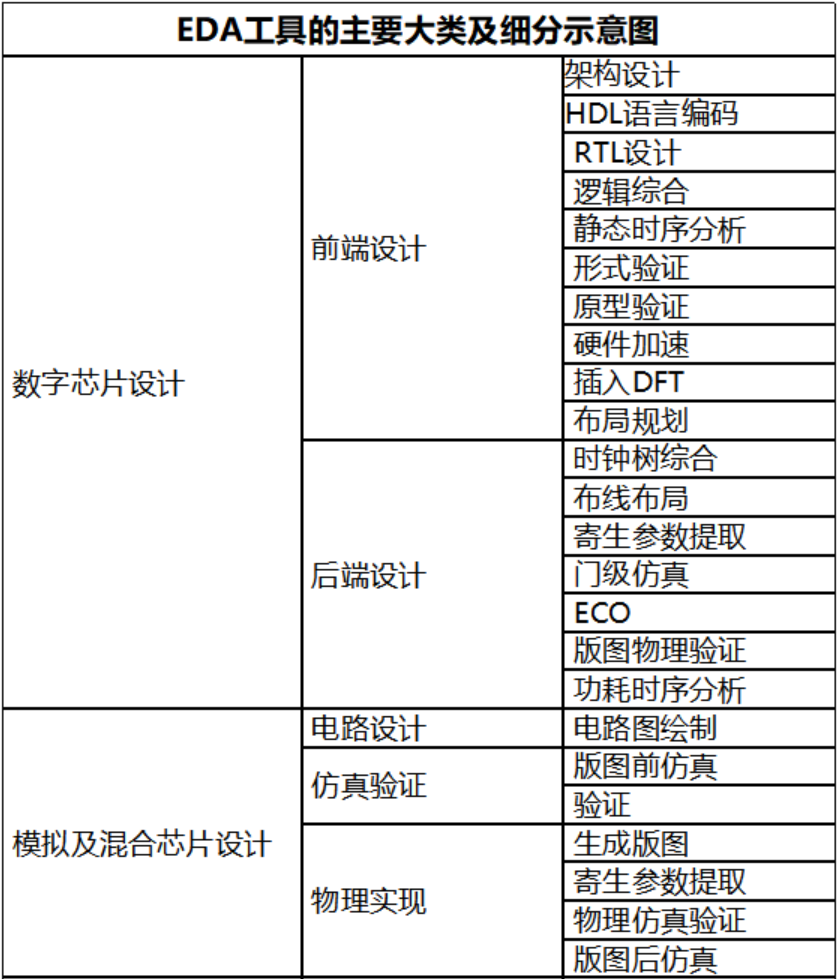

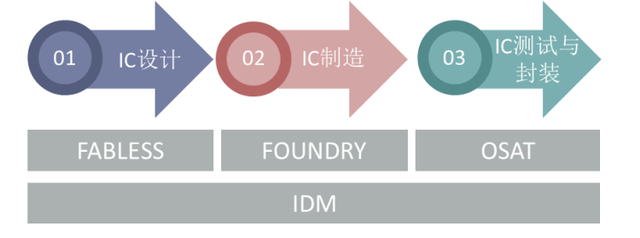

大家需要注意,EDA 并不是一个具体的软件,而是一类软件的统称。它不仅仅用于芯片的设计、验证和仿真,也用于芯片的制造流程。

换言之,EDA 贯穿于芯片的整个研发和生产周期,能够帮助工程师完成大量的细分任务,可以显著提高设计效率、精度以及成功率。

很多人都知道光刻机,也知道光刻机是我们被“卡脖子”的一个关键点。事实上,在 EDA 方面,我们也是被“卡脖子”的,问题同样很严重。

从全球范围内来看,处于 EDA 行业第一梯队的,就是三家公司 ——Synopsys(新思科技)、Cadence(铿腾电子)、Siemens EDA(原 Mentor)。

他们都于上世纪 80 年代创立于美国,目前拥有完整的、全流程的 EDA 产品体系,市场占有率超过 70%,竞争优势非常明显。

国内虽然也有华大九天等一些 EDA 企业,但市场份额较小,和第一梯队的差距较大。

前几天传出新闻,漂亮国那边又在 EDA 上搞事,对我们进行封禁。这也是一件麻烦事。

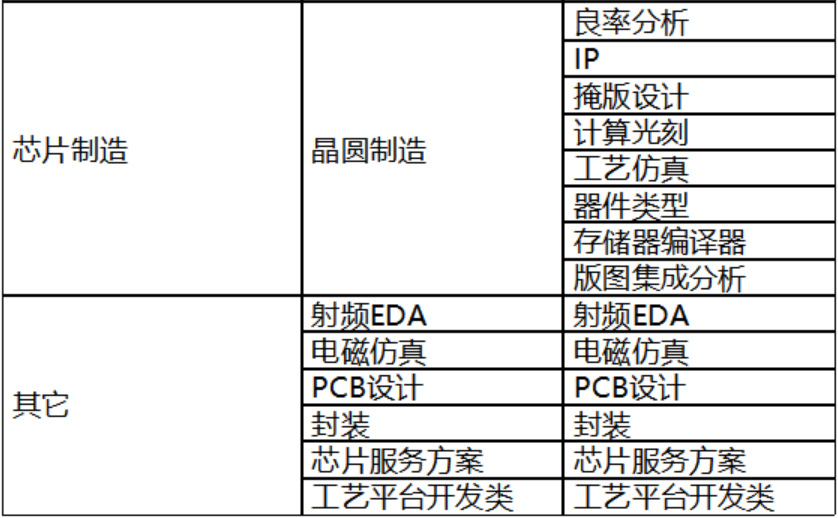

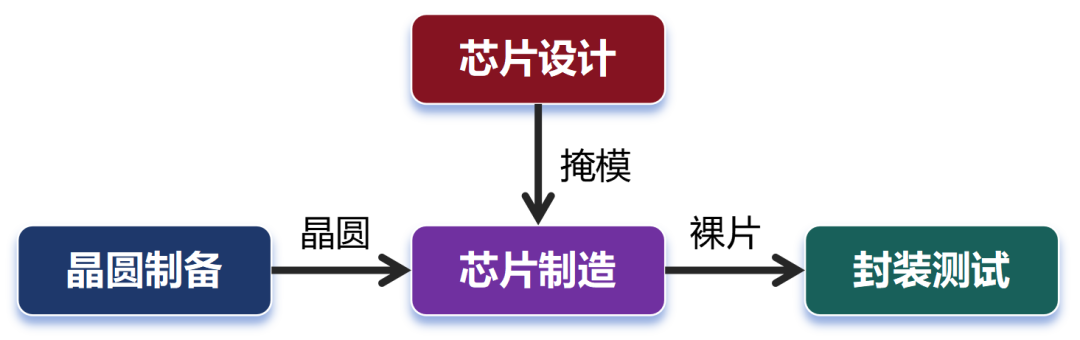

在之前的文章中,小枣君介绍过,芯片的研发和制造有非常明确的分工。

除了极少数公司(IDM,整合元件制造商)设计、制造、封测全都做之外,大部分公司都只做其中一块(Fabless、Foundry、OSAT),或者是某个更加细分的领域。

国内的很多知名芯片公司,例如华为海思、中兴微电子、寒武纪等,都是 Fabless(无晶圆芯片设计企业)。

小米前两天发布了自己的手机 SoC 芯片 —— 玄戒 O1。他们也是 Fabless,只负责设计,芯片制造还是交给了台积电(3nm 工艺)。

芯片设计的难度,由芯片的种类、功能和性能所决定。

数字芯片处理数字信号,通常都可以做很大规模,尤其是现在很多 CPU、GPU、NPU 计算芯片,还有手机 SoC 芯片,结构都极为复杂,晶体管数量极多,设计难度极大,成本也极为高昂。

设计这种高端芯片,往往需要几百甚至几千人的专业技术团队,耗费一年甚至几年的时间,投入上亿甚至上百亿美元的资金。芯片工艺制程越先进,成本就越高。

成本中,包括了专业人才的薪资(芯片设计人才的薪资很高)、EDA 工具的授权费、IP 核(待会会提到)的采购费、设备购买费以及运营费用等。

模拟 / 射频芯片,处理模拟信号,往往是针对一些具体的功能,规模远不如刚才说的高端数字芯片。另外还有一些数模混合信号芯片,例如 ADC(模数转换)、DAC(数模转换),也是针对一些具体应用。这些芯片,大部分相对数字芯片来说简单一些。

对于较为简单的芯片,一些中小型团队,借助目前比较齐全的芯片设计软件工具平台(例如 EDA)和硬件设备,也能够进行自主设计。当然,哪怕是简单的芯片,设计周期大概是 1-1.5 年,耗费资金在百万至千万级。

特别值得一提的是,芯片设计具有极高的风险性。

如果流片(芯片设计最后要进行流片,相当于做一个测试版)失败,损失会非常大(28nm 单次流片需要 1000 万元,7nm 需要超过 1 亿美元)。

直接经济损失还只是一方面。流片失败还会拉长芯片的研发周期,导致错失市场机遇。

严重情况下,流片失败可以直接导致一家公司破产倒闭。

芯片设计,也是有一些“捷径”的。例如采用 IP 核。

IP 核,即知识产权核,代表着一种预先定义、经过验证且可重复使用的模块化功能单元。它是构建大规模集成电路的基础元素。

简单来说,你在设计一个复杂芯片的时候,不必每个部分都从零开始,一些成熟的或通用的功能单元,你就可以直接购买 IP 核,大幅减少芯片设计的工作量。

手机 SoC 芯片的设计理念,其实就来自于 IP 核的复用。

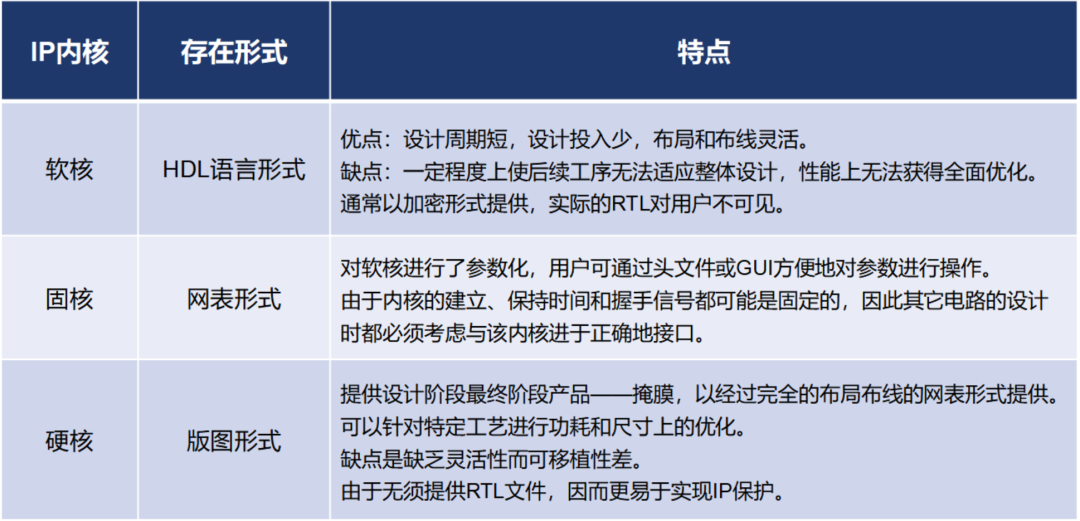

根据特性,IP 核可以分为硬核、固核和软核。具体区别可以参考下面的表格:

目前,芯片 IP 核的主要市场份额也被欧美企业所占据,其中 Arm、Synopsys 和 Cadence 位列市场前三。

大家发现了,Synopsys 和 Cadence 不就是刚才 EDA 三强的第一和第二吗?

没错,搭配捆绑销售,软件授权和 IP 核授权一起卖,效果更好,利润更高。

在芯片设计的产业链中,上游的 EDA 工具和 IP 核授权环节毛利率高达 90% 以上。然而,这些利润基本上都被刚才说的那几家公司所占据。

目前,EDA 工具的国产化率尚不足 5%,高端 IP 核仍严重依赖进口,形势真的是不容乐观。

根据有关机构的数据显示,2020 至 2024 年间,全球芯片设计市场的复合增长率是 9.8%,2024 年市场规模突破 4800 亿美元。中国市场的增长更为惊人,占比从 19% 迅速提升至 28%。

随着整个社会数字化转型的不断推进,还有 AI 浪潮的蓬勃发展,相信包括芯片设计在内的整个芯片产业还会继续高歌猛进。这其中,蕴藏着巨大的商业机会和挑战。

好啦,以上就是今天文章的全部内容。

这期是关于芯片设计的一些基本知识铺垫,算是一个“开胃菜”。

下一期,我们就要进入“正餐”环节,详细介绍芯片设计的完整流程步骤。

敬请关注!

本文来自微信公众号:鲜枣课堂(ID:xzclasscom),作者:小枣君