蓝际水族免安装绿色中文版

57.4M · 2025-11-11

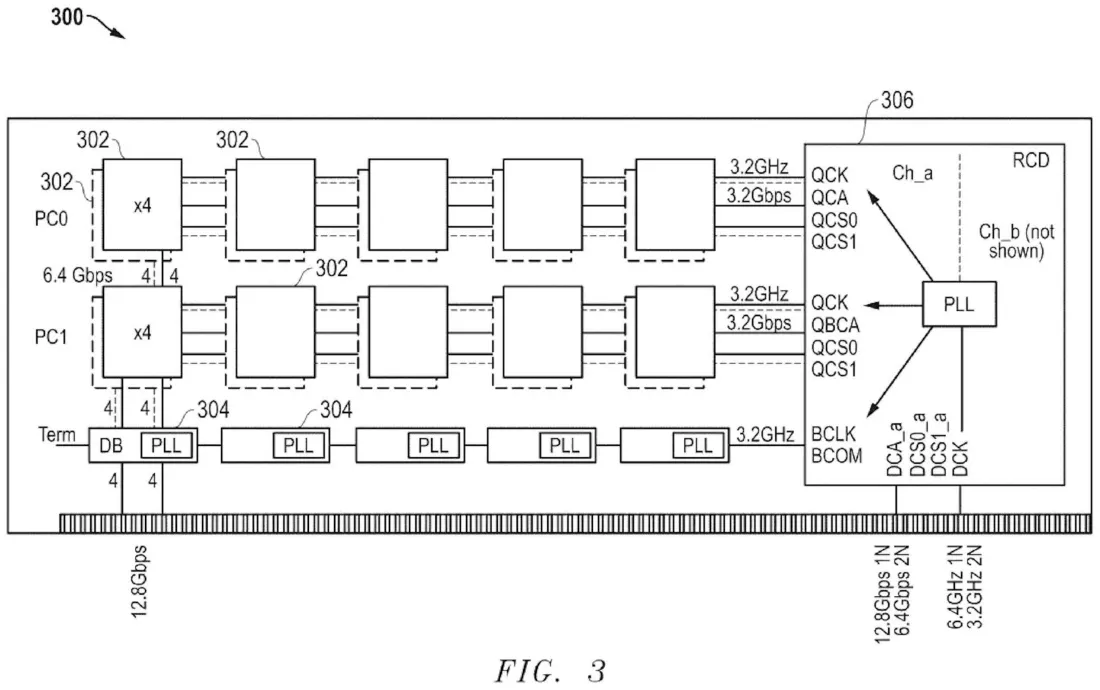

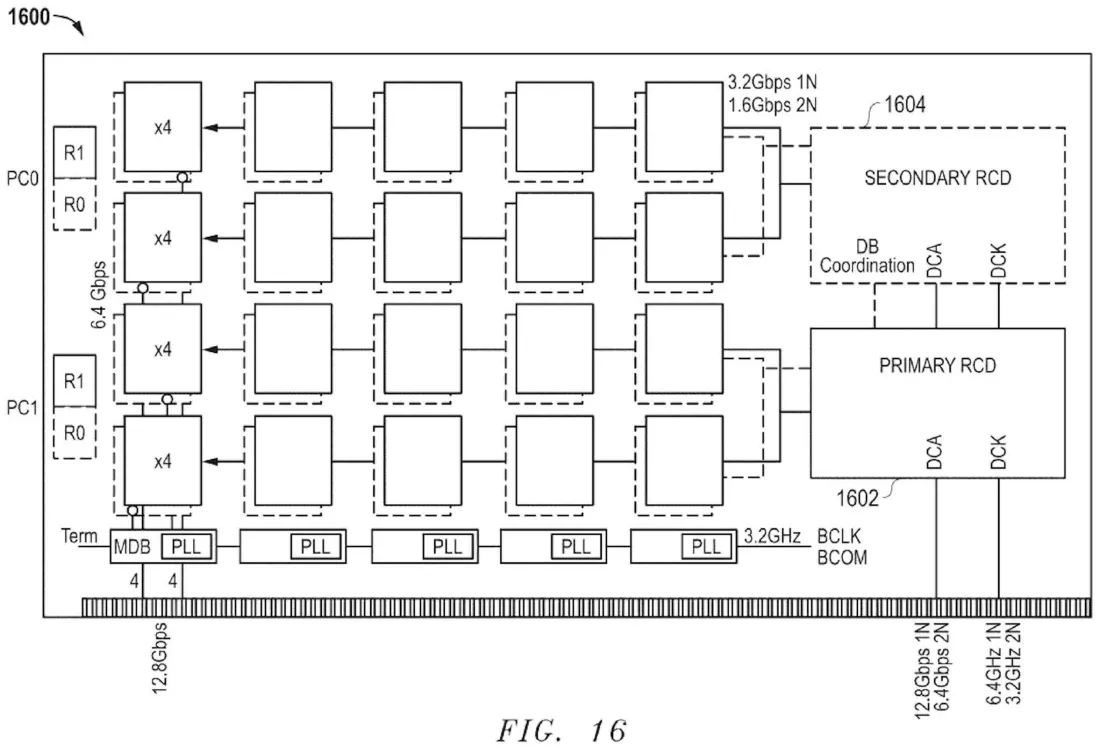

alixixi 9 月 27 日消息,科技媒体 TechSpot 昨日(9 月 26 日)发布博文,报道称 AMD 获批名为“高带宽内存模组架构”的新专利,旨在解决 DDR5 内存面临的性能瓶颈。这项创新设计可将内存总线的传输速度从 6.4 Gbps 翻倍至 12.8 Gbps,同时降低延迟、提升信号完整性。

alixixi援引博文介绍,这项专利在不改变现有 DRAM 芯片基础的情况下,采用高带宽双列直插内存模组(HB-DIMM)方案实现性能提升。具体来说,该设计并非重新研发 DRAM 芯片,而是耦合多个 DRAM 设备与先进的数据缓冲芯片。

通过这种方式,缓冲芯片能够有效管理信号流,让输出性能翻倍,最终将内存总线的传输速度从目前标准的 6.4 Gbps 提升至 12.8 Gbps,实现性能的跨越式增长。

该架构的核心是一个寄存器时钟驱动电路,它能解码内存命令,并利用芯片标识符位进行路由。这种方法允许模组将任务分配给可独立寻址的“伪通道”(pseudo channels),从而实现真正的并行访问,有效突破了传统顺序访问模式对数据吞吐量的限制。这标志着内存访问方式的一次重要革新,为提升系统整体效率奠定了基础。

此外,该系统还支持 1n 和 2n 两种操作模式,为时钟和信号管理提供了高度灵活性,有助于优化时序、确保信号完整性。AMD 还采用了一种简化的非交错传输格式,替代了传统的交错配置,此举旨在进一步降低数据传输延迟。

同时,该设计具备在伪通道模式与四通道(quad-rank)配置之间切换的能力,让其能灵活适应高性能计算等对吞吐量和灵活性有严苛要求的复杂场景。